# **HS-NM5500A**

# **Datasheet**

**V1.2**

**Hasion Electronics Co., Ltd.**

2013-09

# 1. Specification:

- Integrated W5500 and all necessary components within a compact PCB. The PCB is optimized and tested strictly;

- Keep W5500 all features;

- Provide high speed SPI to MCU interface;

- Enable Tx/Rx, Full/Half duplex, Link and Speed drive output;

- Operation voltage 3.3V, I/O pin has 5V tolerance;

- Embedded compact transformer inside RJ-45;

- Interface with two 2.54mm pitch 12 header pins;

- Operation temperature: -20~70

# 2. Photograph

HS-NM5500A has a RJ-45 Jack with transformer inside. The interface to MCU is two pitch 12 header pins.

HS-NM5500A module

Tel: +86-28-86127089 , 86120475 Fax: +86-28-86127039 Website: <a href="http://www.hschip.com">http://www.hschip.com</a>

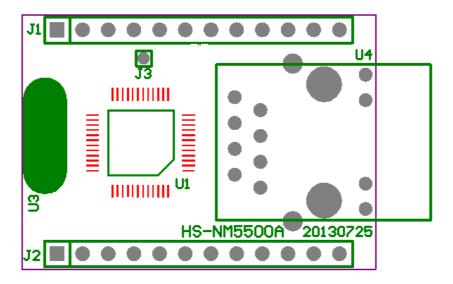

# 3. Layout

HS-NM5500A main components layout

J3 is a test point. In normal operation case, the voltage is 1.2V (Environment temperature at 25 ) at this point.

# **Hasion Electronics Co., Ltd**

#### HS-NM5500A Datasheet v1.2

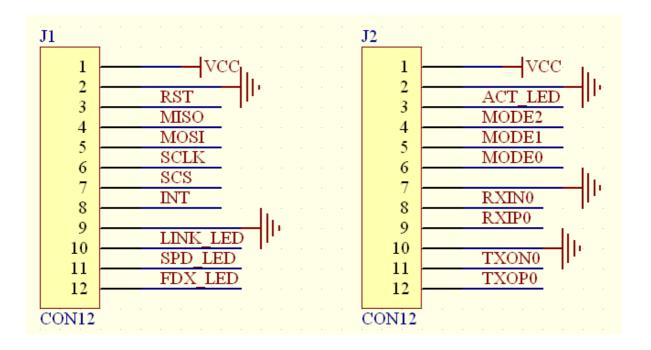

#### Pin definition

#### J1 Pin definition

| Pin   | Name     | Description                                                          |  |

|-------|----------|----------------------------------------------------------------------|--|

| J1-1  | VCC      | Power supply, at range 3.0~3.6V, typically 3.3V                      |  |

| J1-2  | GND      | Power ground                                                         |  |

| J1-3  | /RST     | RESET input, active low. The input RESET should be hold low at least |  |

|       |          | 500us                                                                |  |

| J1-4  | MISO     | SPI Bus, Master In Slave Out                                         |  |

| J1-5  | MOSI     | SPI Bus, Master Out Slave In                                         |  |

| J1-6  | SCLK     | SPI Bus, Clock signal                                                |  |

| J1-7  | /SCS     | SPI Bus, Chip select                                                 |  |

| J1-8  | /INT     | Interrupt output, active low                                         |  |

| J1-9  | GND      | Power ground                                                         |  |

|       | LINK_LED | This shows the Link status.                                          |  |

| J1-10 |          | Low: Link is established                                             |  |

|       |          | High: Link is not established                                        |  |

|       | SPD_LED  | This shows the Speed status of the connected link.                   |  |

| J1-11 |          | Low: 100Mbps                                                         |  |

|       |          | High: 10Mbps                                                         |  |

|       |          | This shows the Duplex status for the connected link.                 |  |

| J1-12 | FDX_LED  | Low: Full-duplex mode                                                |  |

|       |          | High: Half-duplex mode                                               |  |

#### J2 Pin definition

| Pin   | Name    | Description                                                                                             |  |

|-------|---------|---------------------------------------------------------------------------------------------------------|--|

| J2-1  | VCC     | Power supply, at range 3.0~3.6V, typically 3.3V                                                         |  |

| J2-2  | GND     | Power ground                                                                                            |  |

| J2-3  | ACT_LED | It shows that there is Carrier Sense from the active Physical Medium Sub Layer during RX or TX activity |  |

|       |         | Low: Carrier Sense detected                                                                             |  |

|       |         | High: No Carrier Sense                                                                                  |  |

| J2-4  | MODE2   | PHY Operation Select pins. Inner pull up.                                                               |  |

| J2-5  | MODE1   | These pins determine Ethernet PHY operation. For more information,                                      |  |

| J2-6  | MODE0   | please refer to W5500 datasheet.                                                                        |  |

| J2-7  | GND     | Power ground                                                                                            |  |

| J2-8  | TXOP    | HS-NM5500A has no these signals output                                                                  |  |

| J2-9  | TXON    |                                                                                                         |  |

| J2-10 | GND     | Power ground                                                                                            |  |

| J2-11 | RXIP    | HS-NM5500A has no these signals input                                                                   |  |

| J2-12 | RXIN    |                                                                                                         |  |

Tel: +86-28-86127089, 86120475 Fax: +86-28-86127039 Website: <a href="http://www.hschip.com">http://www.hschip.com</a> Page 3

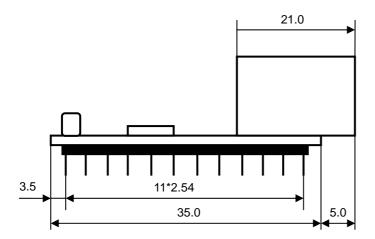

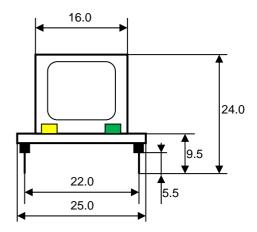

# 4. Dimension (Unit: mm)

Tel: +86-28-86127089 , 86120475 Fax: +86-28-86127039 ©Copyright 2008. All rights reserved.

Page 4

#### 5. Parameters

# 5.1 DC parameters

(Test Condition: Ta = -40 to 85°C)

|                  | (                    |                           |       |      |      |      |

|------------------|----------------------|---------------------------|-------|------|------|------|

| Symbol           | Parameter            | Test Condition            | Min   | Тур  | Max  | Unit |

| $V_{DD}$         | Supply voltage       | Apply VDD, AVDD           | 2.97  | 3.3  | 3.63 | V    |

| $V_{IH}$         | High level input     |                           | 2.0   |      | 5.5  | ٧    |

|                  | voltage              |                           |       |      |      |      |

| $V_{IL}$         | Low level input      |                           | - 0.3 |      | 0.8  | ٧    |

|                  | voltage              |                           |       |      |      |      |

| $V_{T}$          | Threshold point      | All inputs except XI      | 1.30  | 1.41 | 1.53 | V    |

| $V_{T+}$         | Schmitt trig Low to  | All inputs except XI      | 1.53  | 1.64 | 1.73 | ٧    |

|                  | High Threshold point |                           |       |      |      |      |

| V <sub>T</sub> . | Schmitt trig High to | All inputs except XI      | 0.95  | 1.02 | 1.09 | V    |

|                  | Low Threshold point  |                           |       |      |      |      |

| T,               | Junction             |                           | 0     | 25   | 125  | °C   |

|                  | temperature          |                           |       |      |      |      |

| IL               | Input Leakage        |                           |       |      | ±1   | μΑ   |

|                  | Current              |                           |       |      |      |      |

| R <sub>PU</sub>  | Pull-up Resistor     | SCSn, RSTn, PMODE[2:0]    | 62    | 77   | 112  | Kohm |

| R <sub>PD</sub>  | Pull-down Resistor   | RSVD(Pin 23, Pin 38 ~ Pin | 48    | 85   | 174  | Kohm |

|                  |                      | 42)                       |       |      |      |      |

| VoL              | Low level output     | IOL = 8mA,                |       |      | 0.4  | ٧    |

|                  | voltage              | All outputs except XO     |       |      |      |      |

| V <sub>OH</sub>  | High level output    | IOH = 8mA,                | 2.4   |      |      | V    |

|                  | voltage              | All outputs except XO     |       |      |      |      |

| I <sub>OL</sub>  | Low level output     | VOL = 0.4V, All outputs   | 8.6   | 13.9 | 18.9 | mA   |

|                  | Current              | except XO                 |       |      |      |      |

| I <sub>OH</sub>  | High level output    | VOH = 2.4V, All outputs   | 12.5  | 26.9 | 47.1 | mA   |

|                  | Current              | except XO                 |       |      |      |      |

| I <sub>DD1</sub> | Supply Current       | VDD=3.3V, AVDD=3.3V, Ta   |       | 132  |      | mA   |

|                  | (Normal operation    | = 25°C                    |       |      |      |      |

|                  | mode)                |                           |       |      |      |      |

| I <sub>DD2</sub> | Supply Current       | PHY Power Down mode,      |       | 13   |      | mA   |

|                  | (Power Down mode)    | VDD=3.3V, AVDD=3.3V, Ta   |       |      |      |      |

|                  |                      | = 25°C                    |       |      |      |      |

|                  |                      |                           |       |      |      |      |

Tel: +86-28-86127089, 86120475 Fax: +86-28-86127039 Website: <a href="http://www.hschip.com">http://www.hschip.com</a> Page 5

#### **5.2 Power consumption**

(Test Condition: VDD=3.3V, AVDD=3.3V, Ta = 25°C)

| Condition                       | Min | Тур | Max | Unit |

|---------------------------------|-----|-----|-----|------|

| 100M Link                       | -   | 128 | -   | mA   |

| 10M Link                        | -   | 75  | -   | mA   |

| Un-Link (Auto-negotiation mode) | -   | 65  | -   | mA   |

| 100M Transmitting               | -   | 132 | -   | mA   |

| 10M Transmitting                | -   | 79  | -   | mA   |

| Power Down mode                 | -   | 13  | -   | mA   |

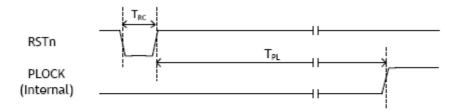

### 5.3 Reset timing

Figure 22. Reset Timing

| Symbol          | Description                       | Min    | Max  |

|-----------------|-----------------------------------|--------|------|

| T <sub>RC</sub> | Reset Cycle Time                  | 500 us | -    |

| T <sub>PL</sub> | RSTn to internal PLOCK (PLL Lock) | -      | 1 ms |

Please refer to W5500 datasheet to get more information.

Tel: +86-28-86127089 , 86120475 Fax: +86-28-86127039 ©Copyright 2008. All rights reserved. Website: http://www.hschip.com

Page 6